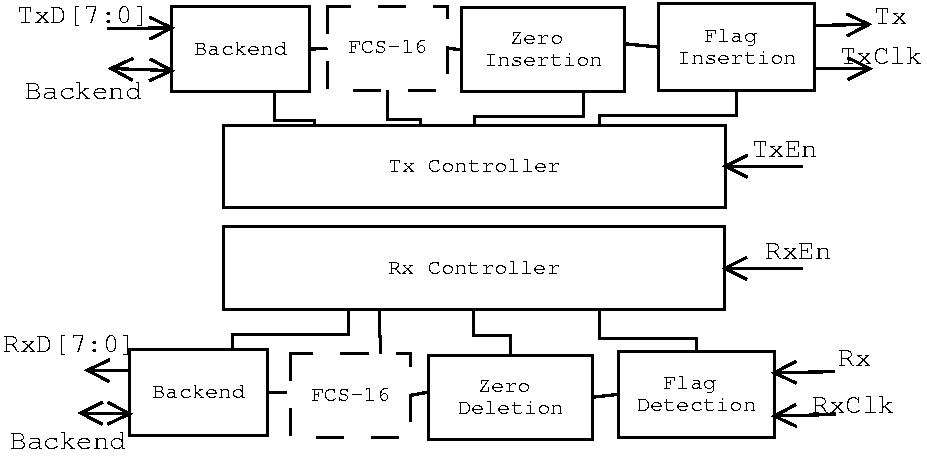

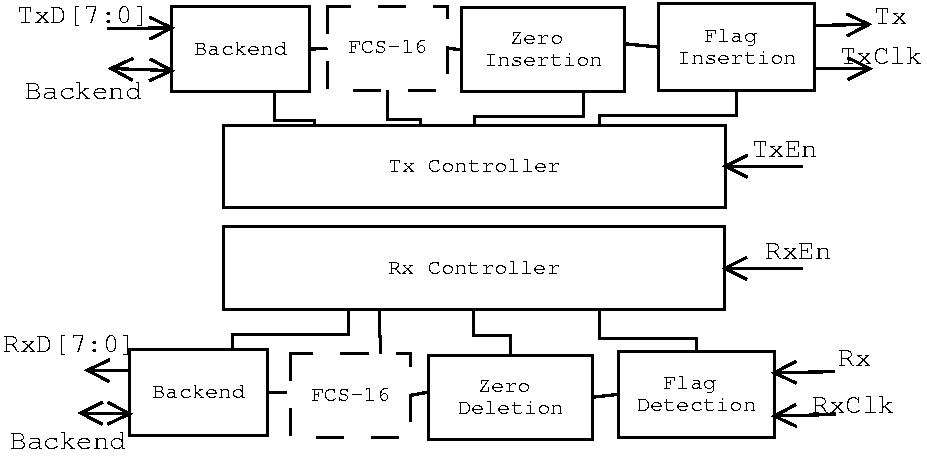

HDLC controller

| Vendor | Device | Size | Frequency | Board Tested | Functional Test | Notes |

| Altera | EP20K100BC356-3 | 108 LCs | 91.48MHz | - | - | No optimization was peroformed, using Quartus II |

| Vendor | Device | Size | Frequency | Board Tested | Functional Test | Notes |

| Altera | EP20K100BC356-3 | 100 LCs | 112.42MHz | - | - | No optimization was peroformed, using Quartus II |

| Vendor | Device | Size | Frequencies (MHz) | Board Tested | Functional Test | Notes |

| Altera | EP20K100BC356-3 | 630 LCs, 2 ESBs | CLK_I=74.02,RxClk=101.86,TxClk=106.42 | - | - | No optimization was peroformed, using Quartus II |

Maintainer(s):

Author(s):

Contact email:

Mailing-List: