# <u>AHB ± WISHBONE BRIDGE</u>

# Table of Contents

| Authors                    | 2  |

|----------------------------|----|

| Copyright & License        | 2  |

| Revision No.               | 2  |

| Disclaimer                 | 2  |

| Introduction               | 3  |

| Limitations of Design      | 3  |

| Synthesizability           | 3  |

| Port Definitions           | 4  |

| Block Representation       | 5  |

| Reset operation            | 6  |

| Write Cycle                |    |

| Read Cycle                 | 8  |

| Write with Wait states     | 9  |

| Inserted by Wishbone Slave | 9  |

| Inserted by AHB Master     | 10 |

| Read with wait states      | 12 |

| Inserted by Wishbone Slave | 12 |

| Inserted by AHB Master     |    |

| Read after Write           | 15 |

| Write after Read           | 16 |

Authors

TooMuch Semiconductor Solutions (info@toomuchsemi.com)

## Copyright & License

Copyright (c) 2007 TooMuch Semiconductor Solutions Pvt Ltd.

Revision No.

1.0

Disclaimer

This source file may be used and distributed without restriction provided that this copyright statement is not removed from the file and that any derivative work contains the original copyright notice and the associated disclaimer.

This software is provided <sup>a</sup>as is<sup>o</sup> and without any express or implied warranties, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. in no event shall the author or contributors be liable for any direct, indirect, incidental, special, exemplary, or consequential damages (including, but not limited to, procurement of substitute goods or services; loss of use, data, or profits; or business interruption) however caused and on any theory of liability, whether in contract, strict liability, or tort (including negligence or otherwise) arising in any way out of the use of this software, even if advised of the possibility of such damage.

#### Introduction

The AHB-Wishbone bridge is an RTL implementation of a synthesisable bridge to interconnect AHB Master to Wishbone Slave.

#### Limitations of Design

- This design will not work for Sequential transfers (ie for wrap and incremental type of transfers).

- No error, retry and split cases have been considered in the design.

- Word size is 32 bits. It can be modified as per requirement.

- All transfers has been considered as non-sequential type.

#### Synthesizability

This code is completely synthesizable. The only care that has to be taken is that the wishbone clock(clk\_i) and reset(rst\_i) signals have been left unconnnected inside the design. The whole design is working on AHB clock and reset signals that should be provided by AHB master.

## Port Definitions

| Port Name | Direct<br>ion | Size | Source      | Description                           |  |  |  |  |  |  |

|-----------|---------------|------|-------------|---------------------------------------|--|--|--|--|--|--|

| Hclk      | in            | 1    | AHB Master  | Bus Clock                             |  |  |  |  |  |  |

| Hresetn   | in            | 1    | AHB Master  | Active Low Sync. Reset                |  |  |  |  |  |  |

| Hwdata    | in            | 32   | AHB Master  | Write data bus                        |  |  |  |  |  |  |

| Hwrite    | in            | 1    | AHB Master  | Read/Write enable                     |  |  |  |  |  |  |

| Hburst    | in            | 3    | AHB Master  | Burst Type                            |  |  |  |  |  |  |

| Hsize     | in            | 3    | AHB Master  | not used                              |  |  |  |  |  |  |

| Htrans    | in            | 2    | AHB Master  | Transfer Type                         |  |  |  |  |  |  |

| Hsel      | in            | 1    | AHB Decoder | Slave select signal                   |  |  |  |  |  |  |

| Haddr     | in            | 16   | AHB Master  | Address bus                           |  |  |  |  |  |  |

| dat_i     | in            | 32   | WB Slave    | Data Bus                              |  |  |  |  |  |  |

| ack_i     | in            | 1    | WB Slave    | To indicate current transfer status   |  |  |  |  |  |  |

| clk_i     | in            | 1    | WB Slave    | unconnected                           |  |  |  |  |  |  |

| rst_i     | in            | 1    | WB Slave    | unconnected                           |  |  |  |  |  |  |

| adr_o     | out           | 16   | Bridge      | Address bus                           |  |  |  |  |  |  |

| dat_o     | out           | 32   | Bridge      | Data bus                              |  |  |  |  |  |  |

| cyc_o     | out           | 1    | Bridge      | To indicate valid bus cycle           |  |  |  |  |  |  |

| we_o      | out           | 1    | Bridge      | Read/Write enable                     |  |  |  |  |  |  |

| stb_o     | out           | 1    | Bridge      | To indicate valid data transfer cycle |  |  |  |  |  |  |

| Hrdata    | out           | 32   | Bridge      | Read Data Bus                         |  |  |  |  |  |  |

| Hresp     | out           | 2    | Bridge      | Response                              |  |  |  |  |  |  |

| Hready    | out           | 1    | Bridge      | To indicate bridge is ready.          |  |  |  |  |  |  |

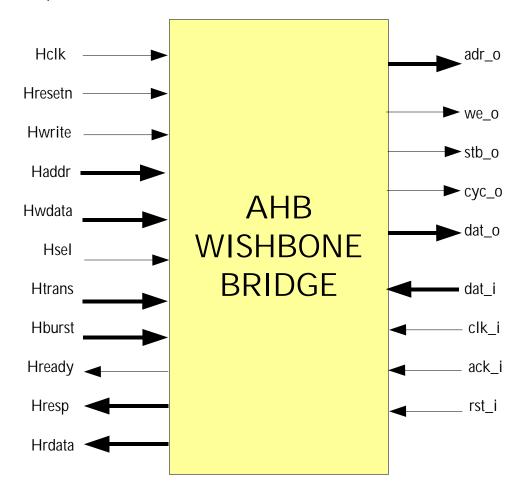

## **Block Representation**

## Reset operation

The AHB reset signal is active LOW and is used to reset the system and the bus. This reset has been asserted and deasserted synchronously after the rising edge of Hclk. The reset is required to be asserted atleast for one clock cycle (AHB Clock).

Fig. 1 : Reset operation

#### Write Cycle

When Hwrite is HIGH, this signal indicates a write transfer and the Master will broadcast data on the write data bus(Hwdata) when Hready signal is HIGH.

- 1) At 1<sup>st</sup> clock edge the address(A1) is sampled by the AHB Slave on Haddr

- 2) This address sampled is transfered synchronously to the wishbone Slave on adr\_o.

- 3) Data(D1) for this address is sampled asynchronously by AHB Slave on Hwdata.

- 4) This data is written into the WISHBONE Slave asynchronously on dat\_o bus.

- 5) At 2<sup>nd</sup> clock edge address(A2) for next transfer is sampled by AHB Slave on Haddr.

- 6) At 2<sup>nd</sup> clock edge address(A1) and data (D1) is sampled by WISHBONE Slave on adr\_o and dat\_o bus respectively.

- 7) At 2<sup>nd</sup> clock edge ack\_i is also asserted.

Fig 2 : Write Cycle

## Read Cycle

When Hwrite is LOW, this signal indicates a read transfer and the Master will receive data on the read data bus (Hrdata) provided the Hready signal is HIGH.

- 1) At 1<sup>st</sup> clock edge the address(A1) is sampled by the AHB Slave on Haddr.

- 2) This address will be transfered synchronously to WISHBONE Slave on adr\_o.

- 3) Data(D1) for this address is sampled asynchronously by WISHBONE Master on dat\_i.

- 4) This data is transfered asynchronously to AHB Master on Hrdata.

- 5) This data (D1) is sampled by AHB Master on 2<sup>nd</sup> clock edge.

- 6) At 2<sup>nd</sup> clock edge address(A2) for next transfer is sampled by AHB Slave on Haddr.

- 7) At 2<sup>nd</sup> clock edge ack\_i is asserted.

Fig. 3 : Read Cycle

## Write with Wait states

#### Inserted by Wishbone Slave

- 1) At 1<sup>st</sup> clock edge the address(A1) is sampled by the AHB Slave on Haddr

- 2) This address sampled is transfered synchronously to the wishbone Slave on adr\_o.

- Data(D1) for this address is taken asynchronously by AHB Slave after 1<sup>st</sup> clock edge on Hwdata.

- 4) This data is latched asynchronously on dat\_o bus.

- 5) Address (A2) is sampled at 2<sup>nd</sup> clock edge.

- 6) Ack\_i signal is pulled LOW by the wishbone Slave after 2<sup>nd</sup> clock edge.

- 7) Hready signal is pulled down asynchronously, to indicate that the AHB Slave and hence wishbone Slave is not ready to complete its current transfer.

- 8) Address(A3) at next rising clock edge is sampled by AHB Slave when ack\_i and hence Hready is asserted again.

- 9) Data (D2) is latched on dat\_o bus when Hready is asserted.

Fig. 4 : Write cycle with wait state inserted by wishbone Slave

#### Inserted by AHB Master

This is when AHB Master is busy, so that it can not continue its next bus transfer operation.

Fig. 5 : Write Cycle with wait state inserted by AHB Master

- 1) At 1<sup>st</sup> clock edge the address(A1) is sampled by the AHB Slave on Haddr

- 2) This address sampled is transfered synchronously to the wishbone Slave on adr\_o.

- Data(D1) for this address is taken asynchronously by AHB Slave after 1<sup>st</sup> clock edge on Hwdata.

- 4) This data is latched asynchronously on dat\_o bus.

- 5) Address (A2) is sampled at 2<sup>nd</sup> clock edge.

- 6) Assert Htrans to <sup>a</sup>busy(01)<sup>o</sup> after 1<sup>st</sup> clock edge.

- 7) At 2<sup>nd</sup> clock edge the bridge will sample the Htrans signal.

- 8) Deassert <sup>a</sup>stb\_o<sup>o</sup> signal synchronously.

- 9) Ack\_i signal will also be deasserted asynchronously by Wishbone Slave in response to stb\_o signal.

- 10) Htrans is asserted to aNon ± Seq (10)<sup>o</sup> transfer type at clock edge after clock edge 4

- 11) At 4<sup>th</sup> clock edge the bridge will sample the Htrans signal.

- 12) Stb\_o is asserted synchronously at clock edge 4

- 13) Ack\_i is asserted asynchronously with response to stb\_o.

- 14) Data (D2) is latched asynchronously on dat\_o bus .

- 15) Address(A3) at 5<sup>th</sup> clock edge is sampled by AHB Slave

## Read with wait states

#### Inserted by Wishbone Slave

|         |  |         |         |                       |                        | uuuuu aaaaa aaaaa aaaaaa aaaaaa aaaaaa aaaaaa |         |      |  |                                        |  |  |

|---------|--|---------|---------|-----------------------|------------------------|-----------------------------------------------|---------|------|--|----------------------------------------|--|--|

|         |  |         |         |                       |                        |                                               |         |      |  |                                        |  |  |

|         |  | Asel=1  |         |                       |                        | * "                                           |         |      |  |                                        |  |  |

|         |  |         |         |                       |                        |                                               |         | " II |  |                                        |  |  |

|         |  |         |         | *                     |                        | Na<br>Na                                      |         |      |  |                                        |  |  |

|         |  |         |         | nikis <sup>2000</sup> | in#8.64/ <sup>00</sup> |                                               | wi<br>W |      |  |                                        |  |  |

| <b></b> |  | a and a | "Blanks |                       |                        |                                               |         |      |  | ······································ |  |  |

Fig. 6 : Read cycle with wait state inserted by wishbone Slave

- 1) At 1<sup>st</sup> clock edge the address(A1) is sampled by the AHB Slave on Haddr

- 2) This address sampled is transfered synchronously to the wishbone Slave on adr\_o.

- Data(D1) for this address is latched asynchronously by wishbone Slave after 1<sup>st</sup> clock edge on dat\_i.

- 4) This data is latched asynchronously on Hrdata bus.

- 5) Address (A2) is sampled at 2<sup>nd</sup> clock edge.

- 6) Ack\_i signal is pulled LOW by the wishbone Slave after 2<sup>nd</sup> clock edge.

- 7) Hready signal is pulled down asynchronously, to indicate that the AHB Slave and hence wishbone Slave is not ready to complete its current transfer.

- 8) Address(A3) at next rising clock edge (6<sup>th</sup>) is sampled by AHB Slave when ack\_i and hence Hready is asserted again.

- 9) Data (D2) is latched on dat\_i bus asynchronously when Hready is asserted.

- 10) Data (D2) is latched on Hrdata asynchronously at the same time.

#### Inserted by AHB Master

This is when AHB Master is busy, so that it can not continue its next bus transfer operation.

Fig. 7: Read cycle with wait state inserted by AHB Master

- 1) At 1<sup>st</sup> clock edge the address(A1) is sampled by the AHB Slave on Haddr

- 2) This address sampled is transfered synchronously to the wishbone Slave on adr\_o.

- Data(D1) for this address is latched asynchronously by wishbone Slave after 1<sup>st</sup> clock edge on dat\_i.

- 4) This data is latched asynchronously on Hrdata bus.

- 5) Address (A2) is sampled at 2<sup>nd</sup> clock edge.

- 6) Assert Htrans to <sup>a</sup>busy(01)<sup>o</sup> after 1<sup>st</sup> clock edge.

- 7) At 2<sup>nd</sup> clock edge the bridge will sample the Htrans signal.

- 8) Deassert <sup>a</sup>stb\_o<sup>o</sup> signal synchronously.

- 9) Ack\_i signal will also be deasserted asynchronously by Wishbone Slave in response to stb\_o signal.

- 10) Htrans is asserted to aNon ± Seq (10)° transfer type at clock edge after clock edge 4

- 11) At 4<sup>th</sup> clock edge the bridge will sample the Htrans signal.

- 12)] Stb\_o is asserted synchronously at clock edge 4

- 13) Ack\_i is asserted asynchronously in response to stb\_o.

- 14) Address(A3) at 5<sup>th</sup> clock edge is sampled by AHB Slave

- 15) Data (D2) is latched asynchronously on dat\_i bus

- 16) Data (D2) is latched asynchronously at the same time on Hrdata bus.

#### Read after Write

- 1) At 1<sup>st</sup> clock edge the address(A1) is sampled by the AHB Slave on Haddr along with Hwrite signal and other control signals.

- 2) This address sampled is transfered synchronously to the wishbone Slave on adr\_o.

- 3) Data(D1) for this address is sampled asynchronously by AHB Slave on Hwdata.

- 4) Hwrite signal is pulled down to LOW (for read operation) after clock edge 1.

- 5) Data(D1) is latched into the WISHBONE Slave asynchronously on dat\_o bus.

- 6) At 2<sup>nd</sup> clock edge address(A2) for next transfer is sampled by AHB Slave on Haddr along with Hwrite signal and is latched synchronously on adr\_o bus.

- 7) we\_o signal is pulled LOW synchronously at 2<sup>nd</sup> clock edge.

- 8) At 2<sup>nd</sup> clock edge address(A1) and data (D1) is sampled by WISHBONE Slave on adr\_o and dat\_o bus respectively.

- 9) Wishbone Slave will latch data(D2) for address (A2) asynchronously on dat\_i bus

- 10) Bridge will latch data(D2) asynchronously on Hrdata at the same time.

Fig. 8: Read after write cycle with wait state inserted by AHB Master during write operation

## Write after Read

- 1) At 1<sup>st</sup> clock edge the address(A1) is sampled by the AHB Slave on Haddr .

- 2) This address will be transfered synchronously to WISHBONE Slave on adr\_o.

- 3) Data(D1) for this address is sampled asynchronously by WISHBONE Master on dat\_i.

- 4) D1 is transfered asynchronously to AHB Master on Hrdata

- 5) Hwrite signal is pulled to HIGH logic(for write operation) after 1<sup>st</sup> rising edge of clock.

- 6) Hwrite logic is transfered synchronously on we\_o port.

- 7) At 2<sup>nd</sup> clock edge address(A2) is sampled by AHB Slave along with Hwrite signal.

- 8) A2 is transfered synchronously from Haddr to adr\_o.

- 9) Bridge transfers data (D2) asynchronously after 2<sup>nd</sup> clock edge from Hwdata to dat\_o.

Fig. 9: Write after Read cycle with wait state inserted by wishbone Slave during read operation