add64.s64 bit integer add

adrlabel.sBranch with link to a subrution and then return

armex.sNormal move and add and load

jump.sA complex program contain MANY MANY MANY kinds of branch

ldrlabel.sload label address

loadcon.sload constant

strcopy.scopy string from source to destination

mul.sperform 1024 multiples

mla.sperform 1024 multiples and add

thumbsub.sThumb program that contain long branch and switch between Thumb and ARM state

block.sa program that contain some LDM?STM instructions

ldm.sa program that contain 2 incremental LDM and two decremental LDM instructions, the last LDM has a load to PC

tblock.sa Thumb program that contain some LDM?STM instructions

mull.sa program that perform MULL and MLAL instructions

2 how to use ARM SDT to generate binary image file

I use the assembly source code come from ARM SDT 2.5 to test my design.

I will describ the process to test them.This process include the following steps:

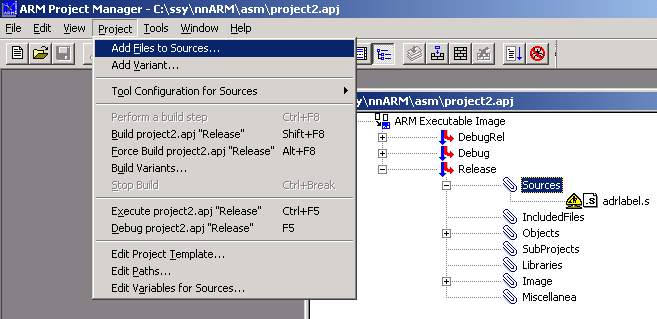

First start the project manager and read in the assembly source code and add it to the project,

And then execute the program and set the starting address of image file to address 0x8000

Then run it and dump the program to a file,please give the start address and the end address.

3 how to use GNU Tools to generate binary image file

First usr "arm-elf-gcc" to compile you program with "-g" flag to generate executable binary file

Then use "arm-elf-gdb" to debug your program, now you can dump out the binary image to a file.

For detail of usage of GNU Tools, please refer to "GNU Tools" page of this site or man page of GNU Tools

4 generate ASCII file for simulator

Now ,No matter what tools you use,you got a binary file of this program, but the verilog simulator can not read it directly, So I write a program to translate it into a ASCII file that can be read in by "readmemh" system task.

This program's name is BIN2ASC,just run it, when it prompt for a file name,input the path and name of your image file,then it will generate a file "ASC" in current dictionary,copy this file to verilog source file dictionary.

In the top level testbench file "tb_system.v", you can find two "readmemh" system task that read this ASCII file.

After all is done just use you verilog simulator to simulate it and compare the result with ARM SDT.